MOS 6502

8 bit

Data bus: 8 Bit, Address bus: 16 Bit

Max.CPU clock rate: 20 kHz to 4 MHz

Instruction set: 65

Package(s): 40 pin DIP

Transistors: 3.510

Process: 8 μm

Area: 21qmm

Predecessor: Motorola 6800

Used in Apple I, Apple II, Commodore PET, VC20, Atari 600XL-120XE

1975-2009

80$-10$

MOS 6510

8 bit

Data bus: 8 Bit, Address bus: 16 Bit

Max.CPU clock rate: 0.985 MHz to 1.023 MHz

Instruction set: 65

Package(s): 40 pin DIP

Transistors: 5.000

Predecessor: Intel 6502

Successor: Intel 8502

Used in Commodore C64

Motorola 68000

16/32 bit

Data bus: 16 Bit, Address bus: 16 Bit, Instructions: 32 Bit

Max.CPU clock rate: 4, 6, and 8 MHz

Instruction set: 65

Package(s): 40 pin DIP

Transistors: 68.000

Process: 4 μm

Area: 44qmm

Predecessor: Intel 6800

Successor: Intel 86010,20,30

Used in many Computers, Apple Macintosh, Apple Lisa, Commodore Amiga, Atari ST

1979-

Z80

8 bit

Data bus: 8 Bit, Address bus: 8 Bit, Instructions: 16 Bit

Max.CPU clock rate: 2.5, 4, 6, and 8, 20MHz

Instruction set: 158

Package(s): 40 pin DIP

Transistors: 8.500

Process: 4 μm

Area: 18qmm

Used in many Computers, most CPM, Schneider Joice, Commodore C128 etc.

1976-

Intel 8085

8 bit

Data bus: 8 Bit, Address bus: 16 Bit

Max.CPU clock rate: 3, 5 and 6 MHz

Instruction set: 80

Package(s): 40 pin DIP

Transistors: 6.500

Process: 3 μm

Area: 20qmm

Predecessor: Intel 8080

Successor: Intel 8086

This is a version build by NEC

1975-1990

Intel Pentium Pro

32 bit

Data bus: 32 Bit, Address bus: 36 Bit

Max.CPU clock rate: 150 MHz to 200 MHz

Front side bus: 60 and 66 MHz

Package(s): Socket 8

Transistors: 5.5 million

L1 cache: 8 KB

L2 Cache: 256-1024 KB

Process: 0.50-0.35 μm

Predecessor: Intel Pentium

Successor: Pentium II Xeon

This is a version with 200 Mhz und 256KB L2 Cache

1995-1998

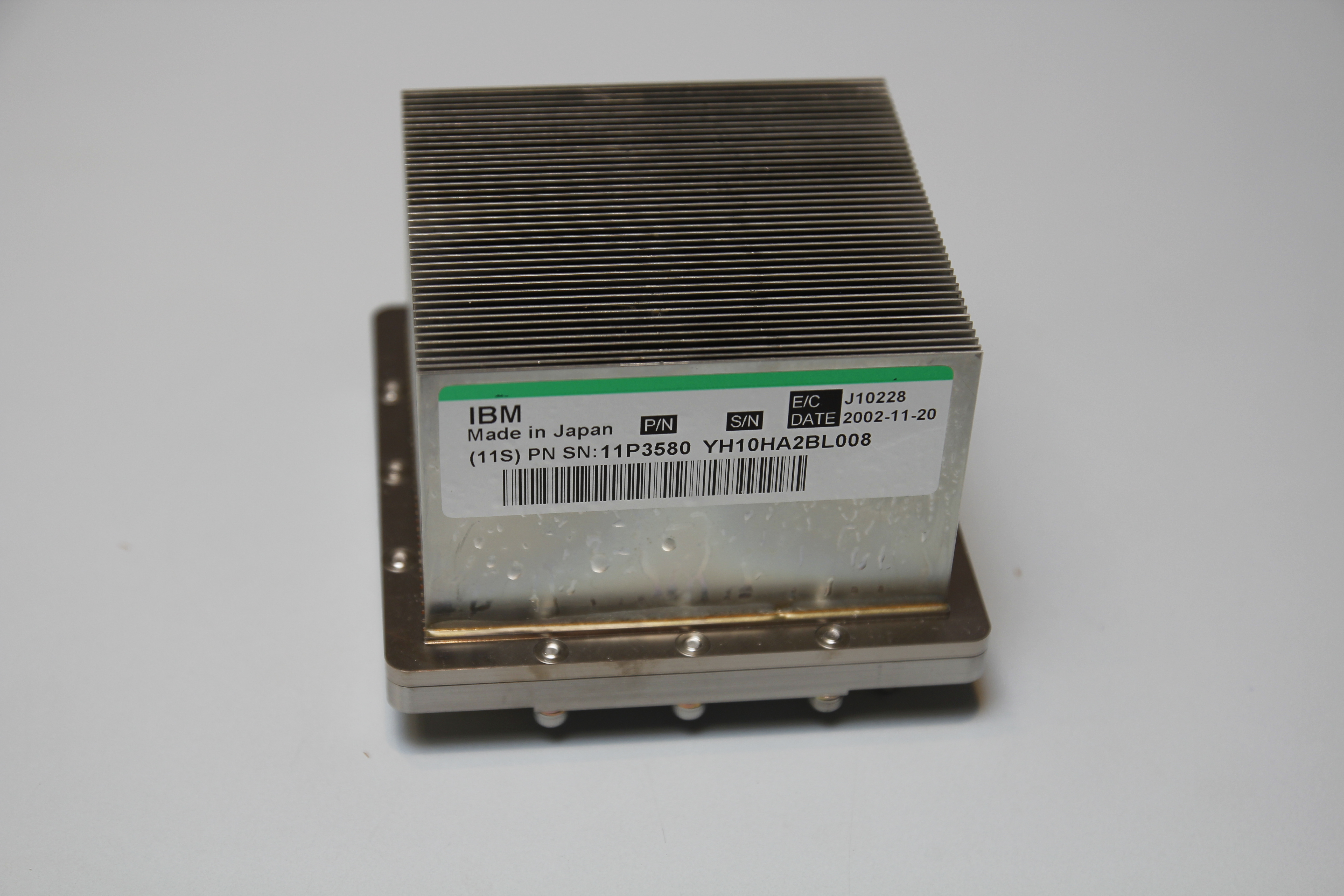

Intel Itanium2

32 bit

Data bus: 32 Bit, Address bus: 36 Bit

Max.CPU clock rate: 900 MHz to 2.53 GHz

Bus Clock rate: 200 MHz

Cores: 1, 2, 4 or 8

Package(s): PAC611

Transistors: 221 million, 25 million for logic

L1 cache: 16 KB

L2 Cache: 256 KB

L3 Cache: 1.5-32 MB

Process: 180 nm

Area: 421-596 qmm

Predecessor: Intel Itanium

This is a "Madison" with 1 Core, 1.5 Ghz and 6MB L3-Cache

2002-2012

Mips R10000

64 bit

Data bus: 64 Bit, Address bus: 40(44) Bit

Max.CPU clock rate: 175 MHz to 250 MHz

Bus Clock rate: 60-100 MHz

Cores: 1, (four-way superscalar or SMP with up to 1000 Cores

Package(s):

Transistors: 6.8 million, 2.4 million for logic

Internal Cache: 32 KB

External Cache: 512 KB to 16 MB

Process: 0.35 μm

Area: 298 qmm

Predecessor: Mips R4000

Successor: Mips R12000-R18000

Used in SGI Indigo2 Impact, SGI Octane, SGI Challange, Origin 2000, Onyx, Onyx2, Siemens SINIX, Tandem

This is a version with 250Mhz (100Mhz bus), 8MB external Cache

1996-1998

3000$

Sun Ultra Sparc II

64 bit

Data bus: 64 Bit, Address bus: 43 Bit

Max.CPU clock rate: 250 MHz to 650 MHz

Bus Clock rate: 100 MHz

Cores: 1

Package(s): LGA-787

Transistors: 5.4 million, 1.35 million for logic

L1 Cache: 16 KB

L2 Cache: 1 to 8 MB

Process: 0.35-0.25 μm

Area: 126-149 qmm

Predecessor: Sun Sparc Ultra

Successor: Sun Sparc Ultra III

This is a version with 450Mhz, 8MB L2 Cache

1997-2004

Sun Ultra Sparc III

64 bit

Data bus: 128 Bit, Address bus: 43 Bit

Max.CPU clock rate: 600 MHz to 1015 MHz

Bus Clock rate: 150 MHz

Cores: 1

Package(s): LGA-1368

Transistors: 29 million, 11 million for logic

L1 Cache: 32-96 KB

L2 Cache: 1 to 8 MB

Process: 0.18-0.13 μm

Area: 126-149 qmm

Predecessor: Sun Sparc Ultra II

Successor: Sun Sparc Ultra IV

This is a version with 1015Mhz, 96MB L1 Cache, 8 MB L2 Cache

2001-2004

Apple PowerPC G4 MPC7450

32 bit

Data bus: 64 Bit, Address bus: 32 Bit

Max.CPU clock rate: 500 MHz to 867 MHz

Bus Clock rate: 100 MHz

Cores: 1

Package(s): 483 pin CBGA

Transistors: 33 million, 10.5 million for logic

L1 Cache: 64 KB

L2 Cache: 256 KB

L3 Cache: 0-2 MB

Process: 0.18 μm

Area: 106 qmm

Predecessor: MPC7410

Successor: MPC744x

Manufacturer: Motorola

This is a version with 733Mhz

2001-

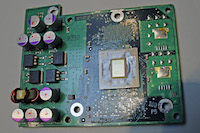

IBM Power3-II

64 bit

Max.CPU clock rate: 375 MHz to 450 MHz

Bus Clock rate: 166-250 MHz

Cores: 1

Transistors: 23 million

L1 Cache: 64+32 KB

L2 Cache: -16 KB

Process: 0.22 μm

Area: 170 qmm

Predecessor: IBM Power3

Successor: IBM Power4

Manufacturer: IBM

This is a version with 1 Core and 400Mhz (bus 250Mhz)

2001-

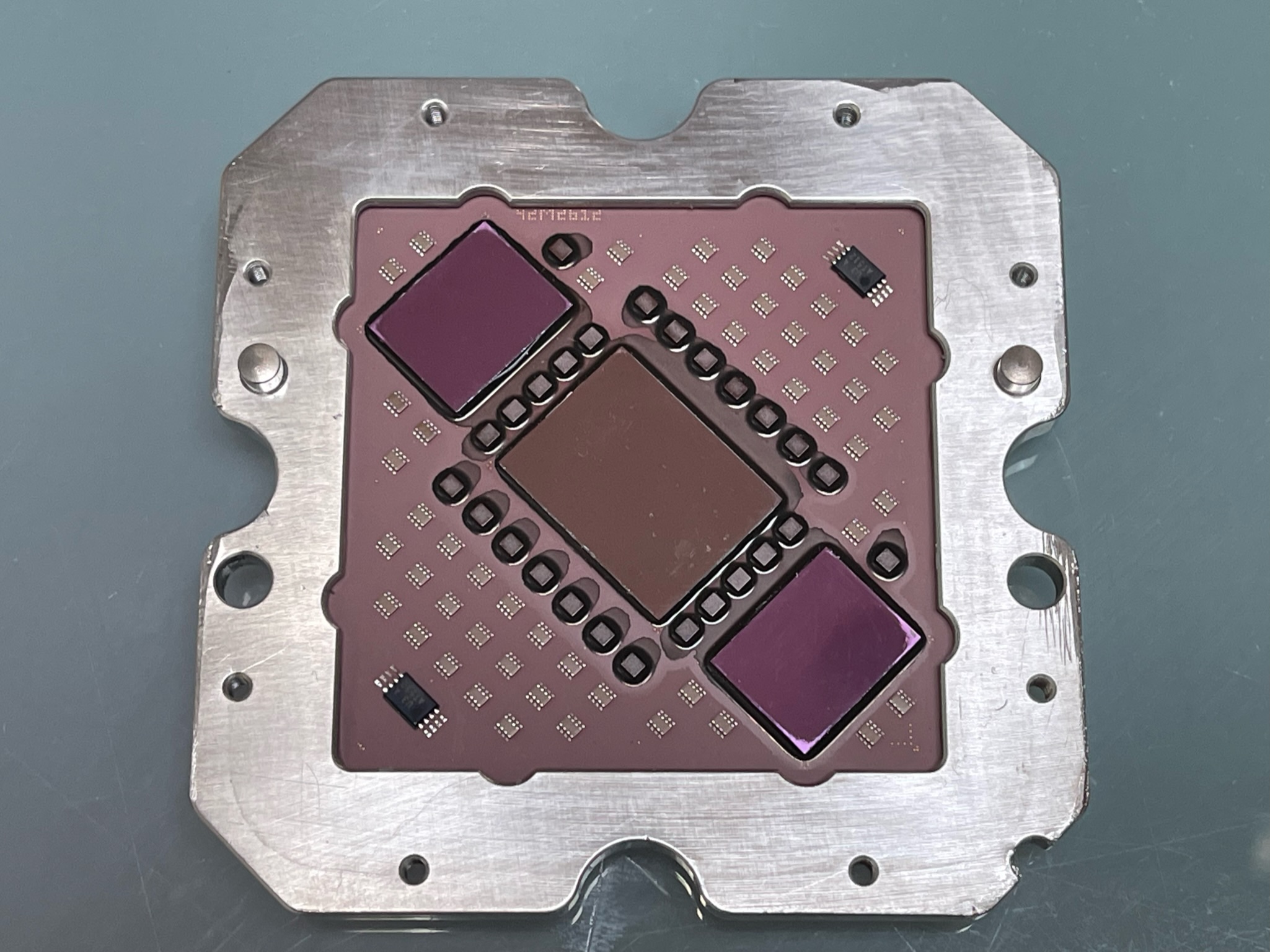

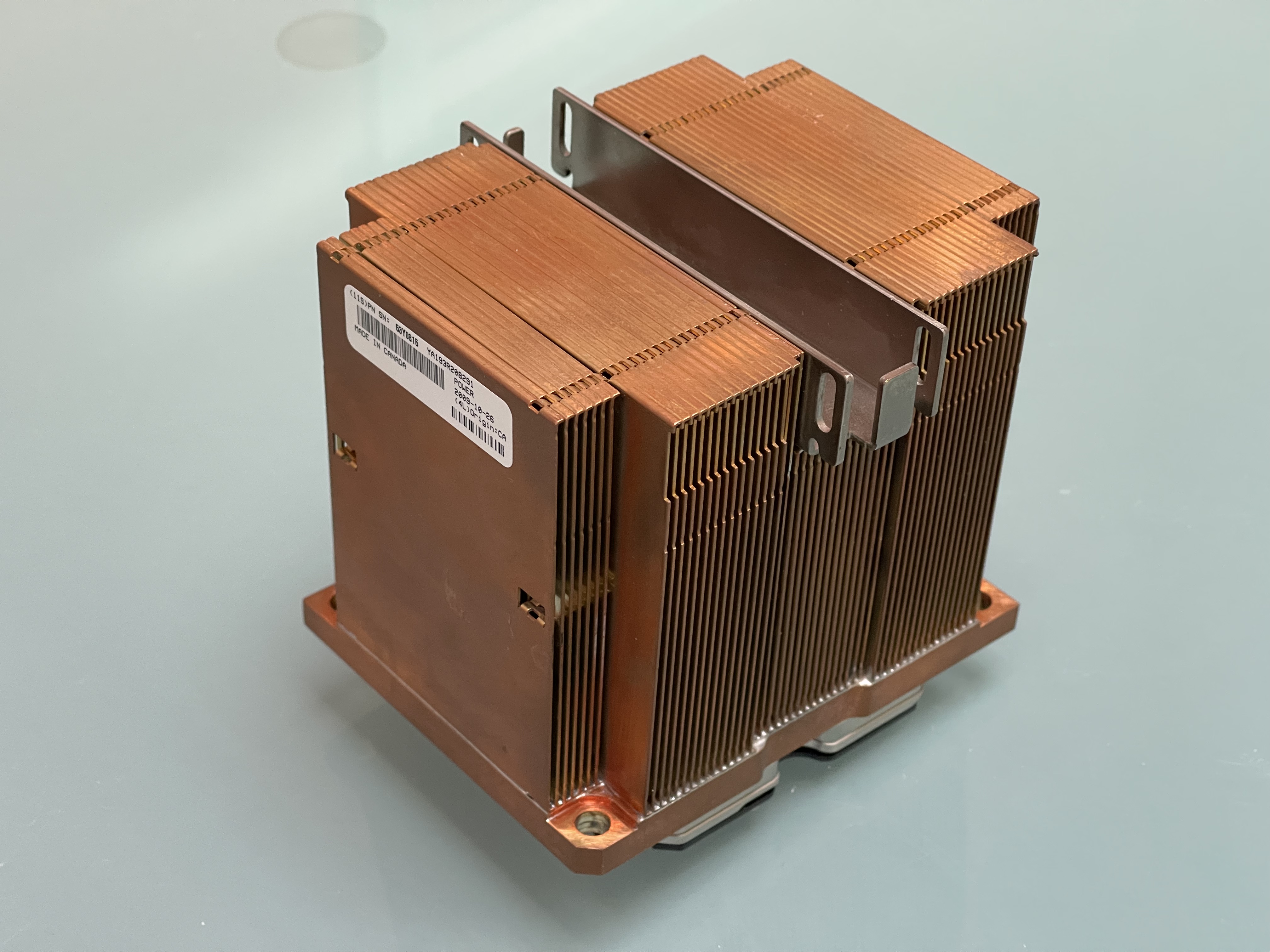

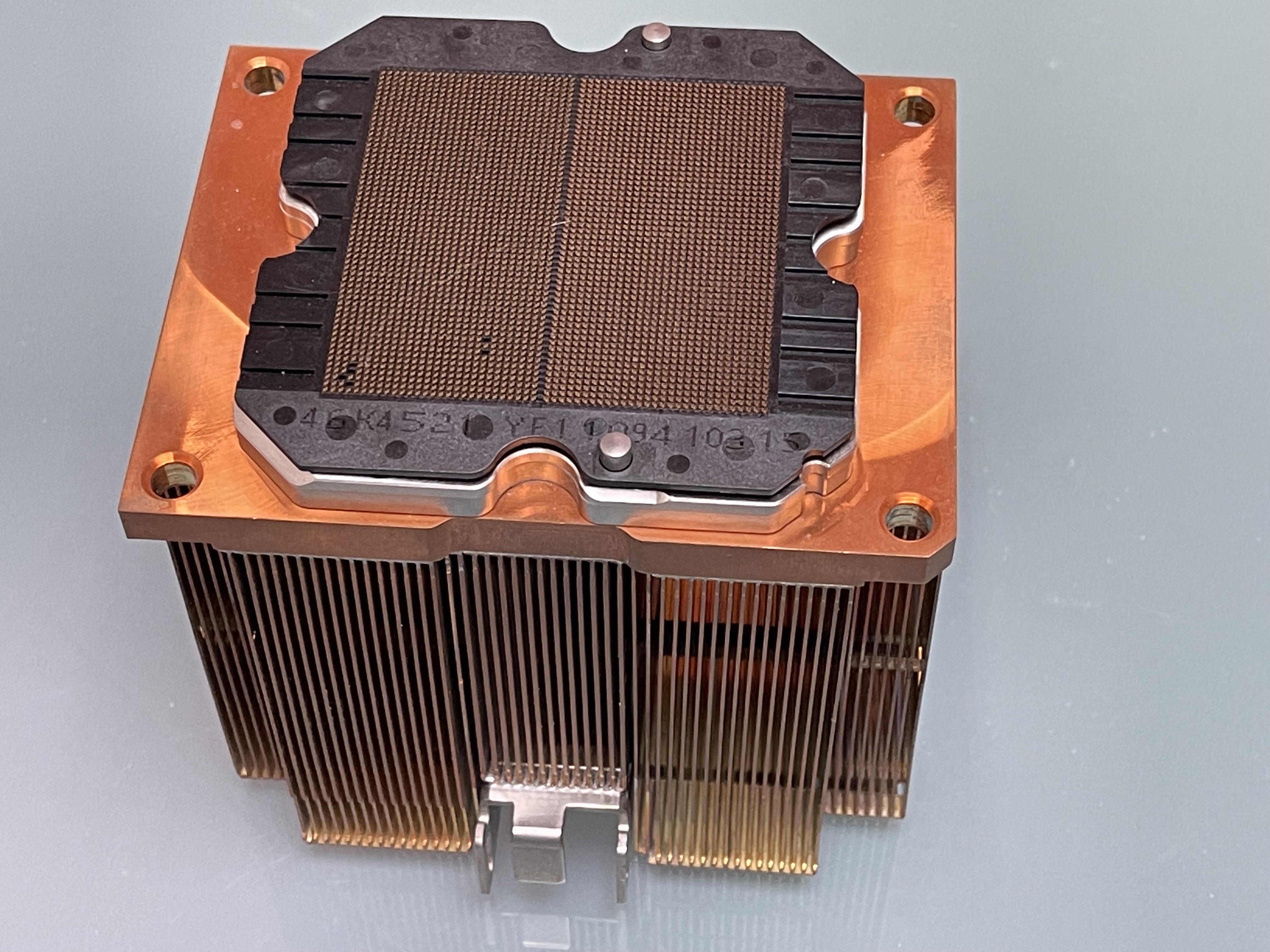

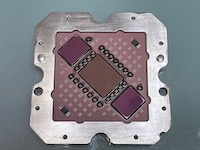

IBM Power5 MCM

64 bit

Max.CPU clock rate: 2.3 GHz

Cores: 8, (2/Die, 4 Proc-Dies, 4 L3-Dies, SMP: 64 Cores

Transistors: 276 million per die, hole MCM: 1.104 Billion

L1 Cache per die: 32+32 KB/core

L2 Cache per die: 1.875 MB (3 x 640 KB)

L3 Cache: 144 MB (4x36MB)

Process: 130-90 nm

Area: 389 mm2/die, 95x95mm

Predecessor: IBM Power4

Successor: IBM Power6

Manufacturer: IBM

This is a 8-Core-MCM containing four POWER5 dies and four 36 MB L3 cache dies

2004-2005-

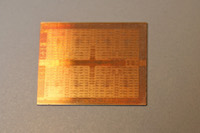

IBM Power6 MCM from IBM P595

64 bit

Max.CPU clock rate: 5 Ghz

Cores: 2 per Sockel, SMP-Nodes: 64 Cores

Transistors: 790 million

L1 Cache: 64+64 KB

L2 Cache: 8 MB (2 x 4MB)

L3 Cache: 2x32 MB

Process: 65 nm

Area: 341 mm2/die, 61x61mm

Predecessor: IBM Power5

Successor: IBM Power7

Manufacturer: IBM

This is a 8-Core-MCM from IBM-P595, containing four POWER6 dies and four 36 MB L3 cache dies

2007-2008-

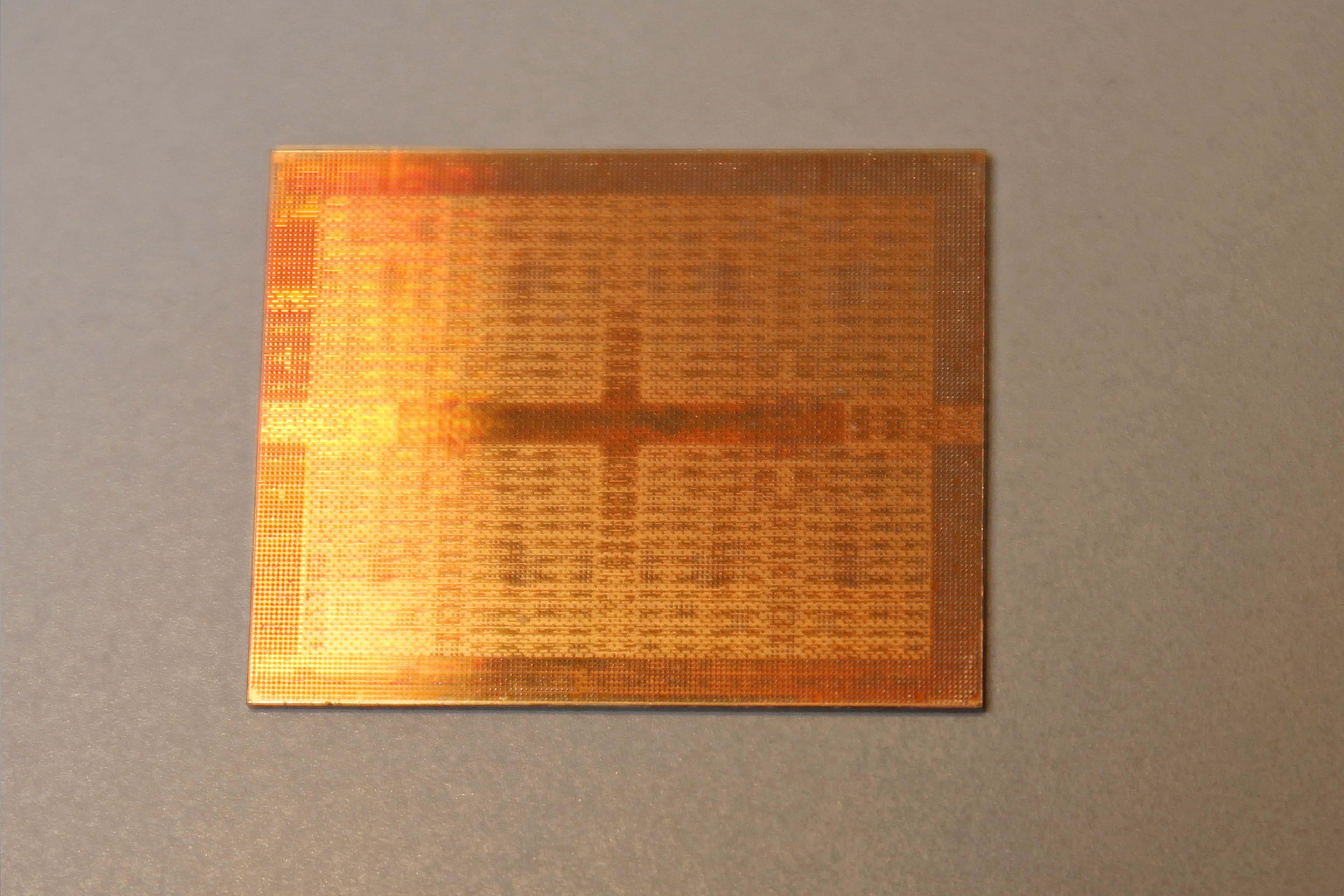

IBM Power7

64 bit

Max.CPU clock rate: 2.4 GHz to 4.25 GHz

Cores: 4,6,8

Transistors: 1.2 billion

L1 Cache: 32+32 KB/core

L2 Cache: 256 KB/core

L3 Cache: 32 MB

Process: 45 nm

Area: 567qmm

Predecessor: IBM Power6

Successor: IBM Power8

Manufacturer: IBM

This is a 4-Core-Chip

2010-

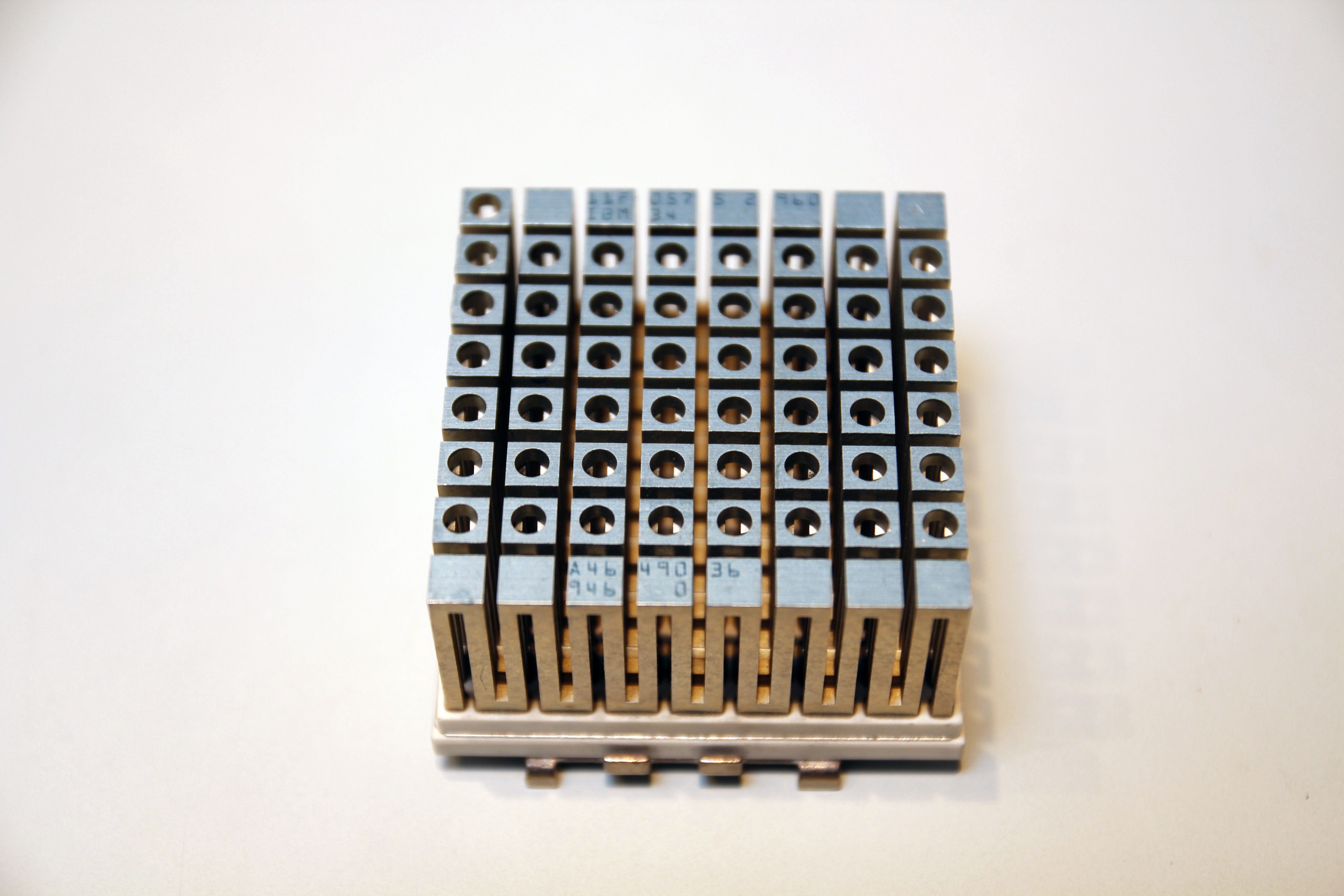

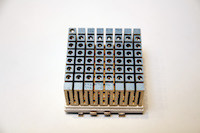

IBM Mainframe 4381

32 bit

IBM 4381 Mainframe P-13 Processor

This is a Part of the Processor-MCM from a IBM 4381.

The IBM 4381 was an IBM/370(XA)-System

maximal Memory: 64MB

68ns internal processor cycle time,

29 logic chips mounted

Operating Systems: VSE,VM/370, MVS/370

1985-

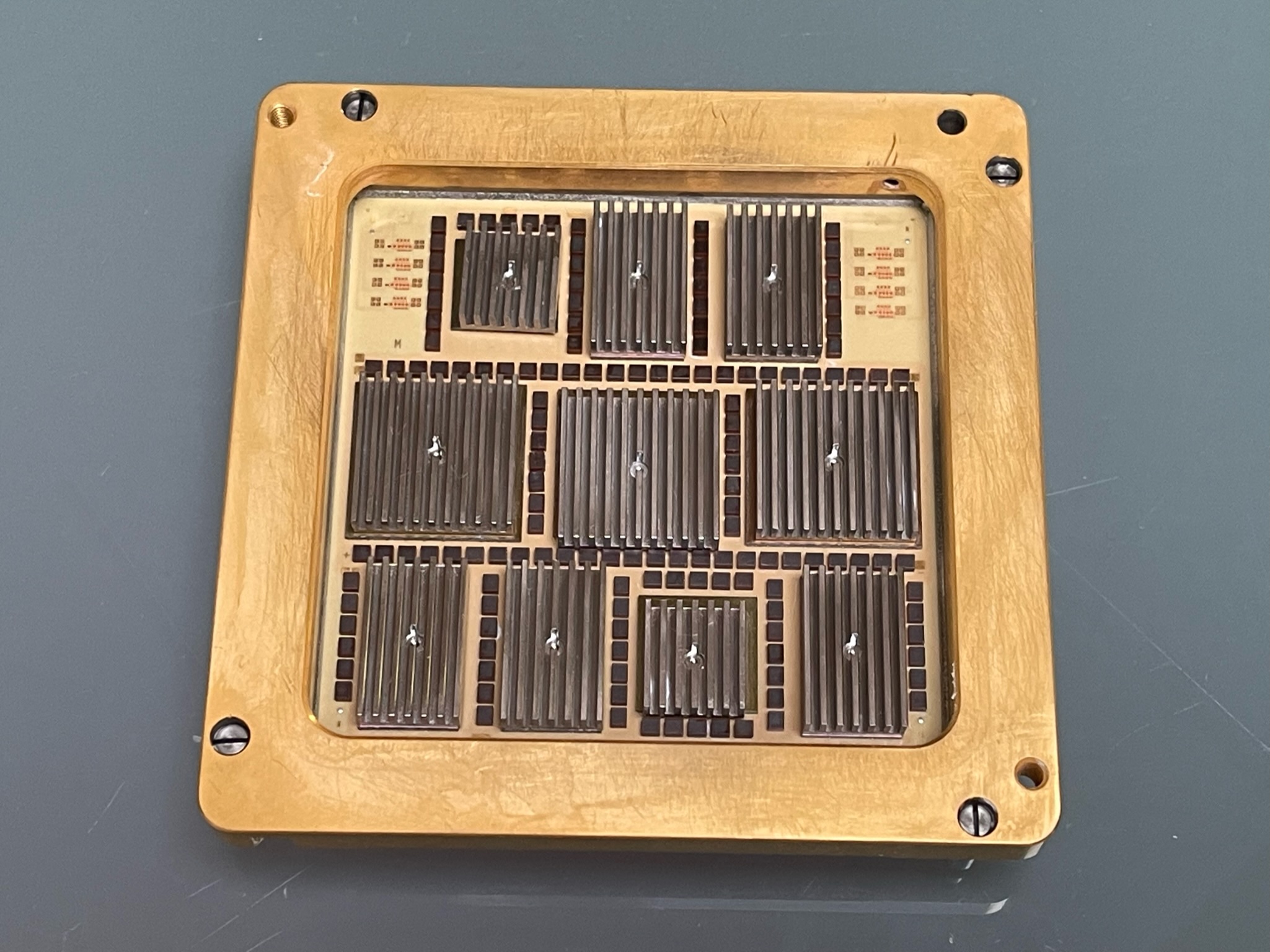

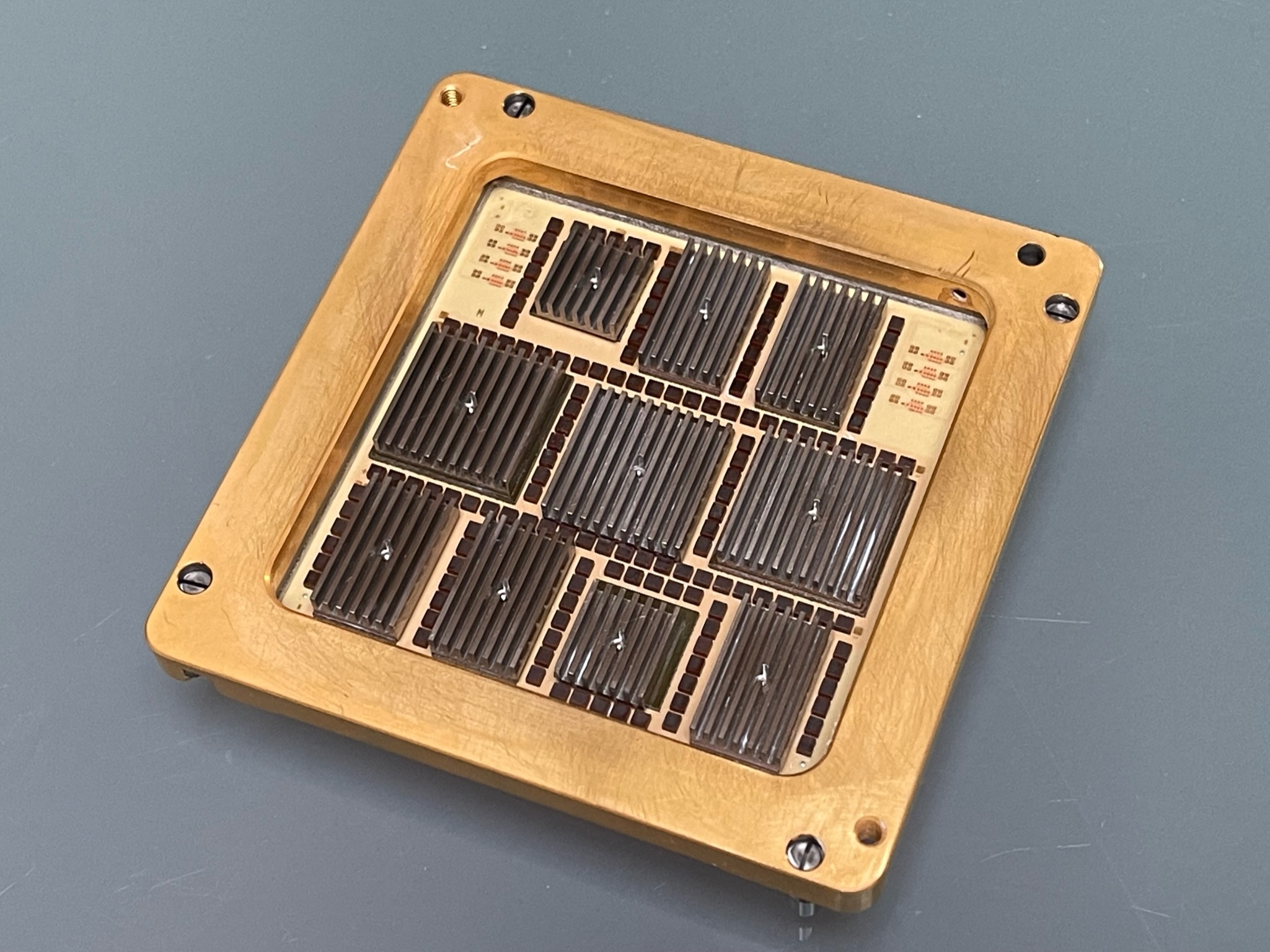

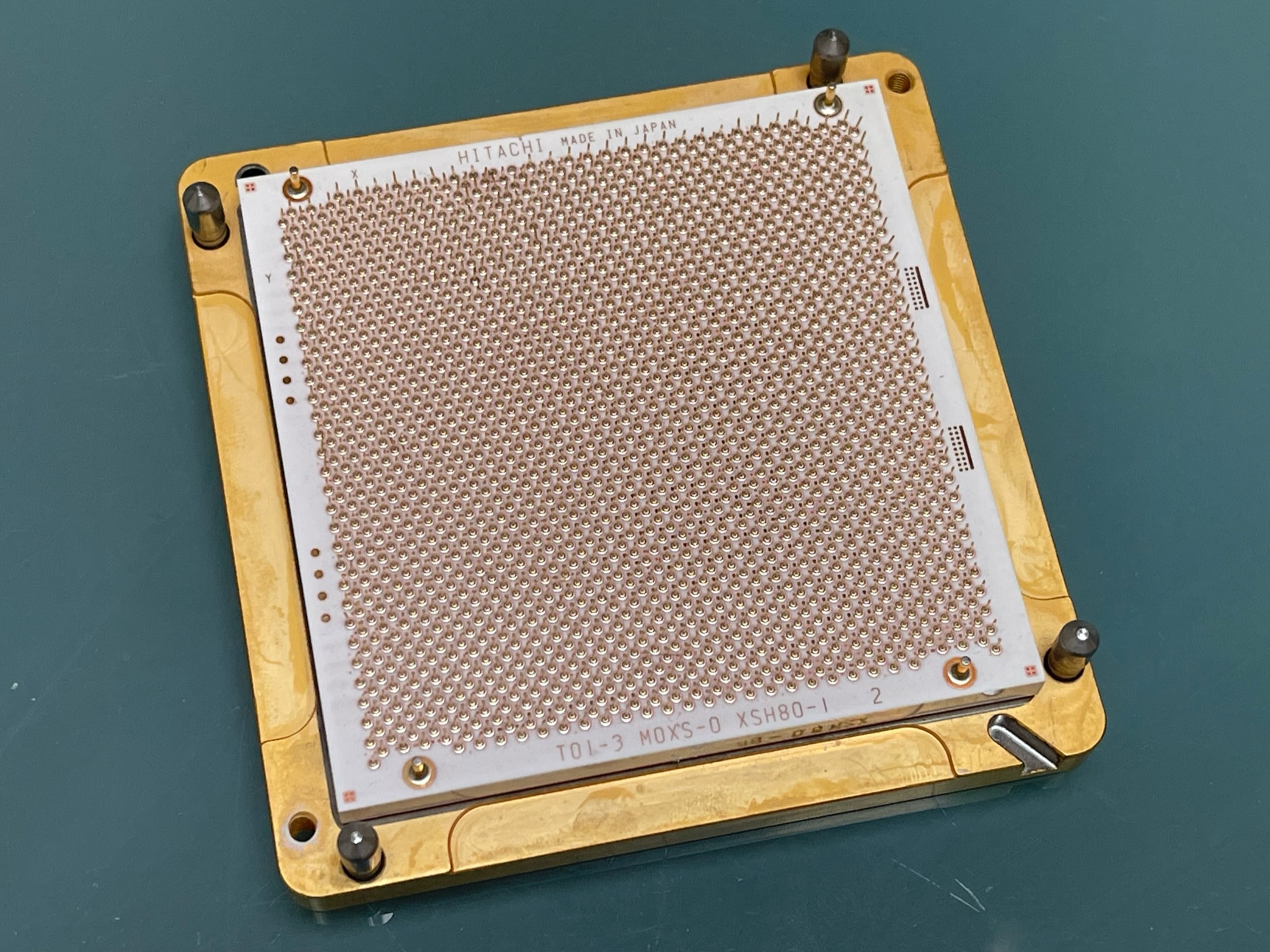

IBM Z8, Mainframe 2066 / Z800

64 bit

The processor-MCM of the IBM 2066br>

includes 10 Chips (5 Cores, 2 L2-Cache-Chips)

Transistors: 690 million (44 million per Core, 237 per L2)

Cores: 5

L1 Cache: 2.5MB (512KB per Core)

L2 Cache: 8 MB

Process: 18 nm

The IBM 2066 was a zSeries-System

Operating Systems: VSE,z/VM, z/OS

Produced by Hitachi

2002-2005

MOS 6502

MOS 6502